发布时间:2024-03-06 来源:芯智讯-浪客剑

2023年10月,日本光刻机大厂佳能(Canon)正式发布了基于纳米压印技术(NIL)的芯片制造设备FPA-1200NZ2C,为生产先进制程芯片开辟出一条成本更低的全新路径。据外媒报道称,美光近日在一场演讲当中介绍了如何将纳米压印技术用于DRAM生产的细节,这似乎也预示着美光将会率先采用佳能的NIL设备用于DRAM芯片的生产,以便进一步降低DRAM的制造成本。

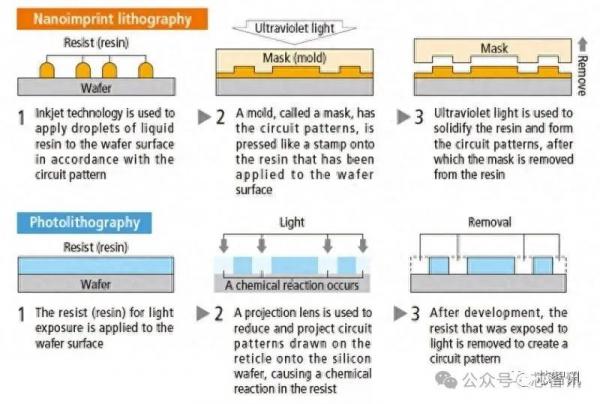

资料显示,佳能力推的纳米压印技术并不是利用传统的光学图像投影的原理将集成电路的微观结构转移到硅晶圆上,而是更类似于印刷技术,即直接通过压印形成图案。在晶圆上只压印1次,就可以在特定的位置形成复杂的2D或3D电路图,不仅非常的便捷,还能在无需EUV光刻机支持的情况下实现5nm制程的,同时还能极大的降低设备采购成本及芯片制造成本。

目前5nm制程的先进半导体制造都需要依赖于EUV光刻机来进行制造,主要EUV光刻机则是由ASML所垄断,单台价格约1.5亿美元。对于接下来更为先进的2nm及以下制程的芯片,ASML也推出了成本更为高昂的High-NA EUV光刻机,单台价格或将超过3亿美元,这也使得尖端制程所需的成本越来越高。

相比之下,佳能的目前纳米压印技术将可以使得芯片制造商不依赖于EUV光刻机就能生产最小5nm制程节点的逻辑半导体。佳能半导体设备业务部长岩本和德此前还曾表示,如果改进光罩,纳米压印甚至可以生产2nm先进制程的芯片。佳能的纳米压印技术或许将有机会帮助佳能缩小其与ASML的差距。

更为关键的是,佳能的纳米压印设备成本和制造成本都远低于ASML的EUV光刻机。岩本和德表示,客户的成本因条件而异,据估算1次压印工序所需要的成本,有时能降至传统曝光设备工序的一半。而且,因为纳米压印设备的规模较小,在研发等用途方面也更容易引进。据了解,采用纳米压印技术,将可使得整体的设备投资降低至EUV光刻产线设备的40%水平。

虽然佳能并未公布其纳米压印设备的定价,但是,佳能CEO御手洗富士夫此前曾表示,该公司的纳米压印设备的“价格将比ASML的EUV光刻机低一位数(即仅有10%)”。

根据佳能此前透露的信息显示,FPA-1200NZ2C将会在2024年至2025年间正式出货。